Department of Computer Science 12

The focus of research at the chair for Hardware/Software Co-Design is the systematic design (CAD) of embedded hardware/software systems.

The perhaps best known example of such a device is the smartphone, but there are many other such everyday items that employ them. Without even realising it, we are surrounded by a wide variety of products that are build with these systems – everything from radio alarm clocks to fully automated coffee machines and even automobiles. They have each been constructed for use for a certain purpose or are optimised for operation in a specific application. A mobile phone, for instance, needs to be such that it can provide outstanding performance while consuming as little power as possible.

The development of these systems, the parameters that need to be taken into account, the appropriate technologies, programming languages (SystemC, C++, Simulink, etc.) and compilers that should be used or require to be developed or adapted – these are the aspects that are at the core of our work.

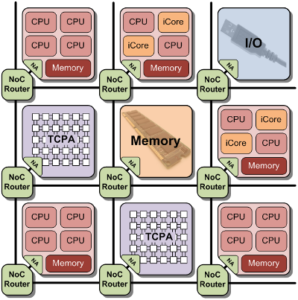

The production techniques now available for the manufacture of electronic circuits make it possible to employ a wide array of embedded system architectures. State-of-the-art mobile phones already utilise four or more processor cores. Several thousand logic units run in parallel in the latest graphics cards. These systems based on several heterogeneous processor or logic units on a single chip are referred to as multiprocessor systems-on-chip (or MPSoC for short).

The following example shows a 64-processor chip called ALPACA, developed at the chair and manufactured in 22 nm. The chip has an enormous computing power of up to 384 billion operations per second with an electrical power consumption of less than 3 W. The chip is particularly suitable for accelerating applications in signal and image processing, machine learning and scientific computing. The following video shows ALPACA in action.

https://www.youtube.com/watch?v=rG8SrT6orUQ

Special compilers are needed to make optimum use of these architectures. A compiler translates a program code in a programming language that can be read by humans (e.g. C++) into a machine code executable by the target system (e.g. for optimum utilisation of the extensive parallelism offered by a graphics card).

In the field of reconfigurable computing, we undertake research aimed at optimising and enhancing these types of systems in order to, for example, enhance the reliability, security and availability of nanoelectrical circuits.

This is achieved by exploiting the potential of FPGAs. These are chips that are not produced for one specific application but are instead re-programmable. When creating an embedded system, it is possible to decide which aspects of functionality are to be executed through the hardware and which through the software; the result in this case is a hardware-software co-design. We investigate which blocks of these FPGAs can be reconfigured during run-time without disrupting operation. One potential application of these would be to make it possible for an automobile component (the one that controls the indicators or the ABS, for example) to take over another component’s function if the latter were to fail.

For the purpose of algorithm and combinatorial optimisation, we also concentrate on developing efficient algorithms (program operations) for local and global search and multi-objective optimisation processes and their applications. A good example of this is the system used for room planning by the university’s Faculty of Engineering. Teaching staff need to find rooms for lectures and seminars that meet certain requirements with regard to room size, availability and time of day, for example. The process we have developed for this supplies perfect results very quickly.